6.7 PROBLEMS

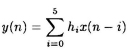

- Consider the 6-tap FIR filter

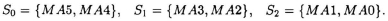

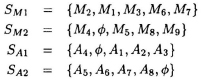

implemented using data-broadcast form shown in Fig. 6.25. This filter is implemented using folding factor 2 with folding set

(a) Design the folded architecture.

(b) Construct a schedule corresponding to the folded architecture and verify that the folded architecture generates the desired filter output samples.

Fig. 6.25 A 6-tap data-broadcast FIR filter for Problem 1.

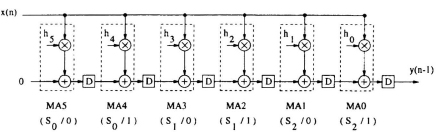

Fig. 6.26 The DFG to be folded in Problem 2.

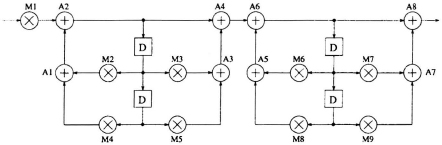

- Perform retiming for folding on the DFG in Fig. 6.26 so that the folding sets shown below result in nonnegative edge delays in the folded architecture. Assume that the folding factor N = 5, and assume that each multiplier is pipelined by 2 stages and each adder is pipelined by 1 stage. Each operator is clocked with clock period of one u.t. The multiplication operation requires 2 u.t. and the addition operation requires 1 u.t. Note that ϕ represents a null operation.

- Fold the retimed DFG obtained in Problem 2 using the folding ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.