Note 54. Polyphase Decimators

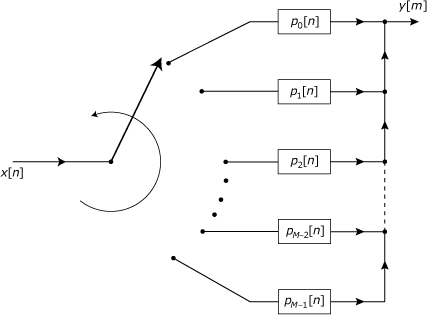

An M-to-1 decimator can be implemented using the polyphase structure shown in Figure 54.1. If h[n] is the response for the decimation filter when implemented in one of the conventional single-stage structures presented in Note 32, then each individual pρ[n] in Figure 54.1 is a different downsampled version of h[n] obtained as

54.1

![]()

for

n = 0, 1, 2,...,(N/M – 1)

r = 0, 1, 2,...,(M – 1)

Figure 54.1. An M-to-1 decimator implemented as a polyphase structure with a commutator

54.1. Why It Works

Consider a conventional ...

Get Notes on Digital Signal Processing: Practical Recipes for Design, Analysis and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.