4.11 LOOPS AND DECISION-MAKING STATEMENTS

Loop statements are a category of control structure that allow a designer to specify repeating sequences of behavior in a circuit. There are three primary types of loops in VHDL: for loops, while loops, and infinite loops. VHDL also provides if–then–else and case statements to implement control structures.

4.11.1 For Loop

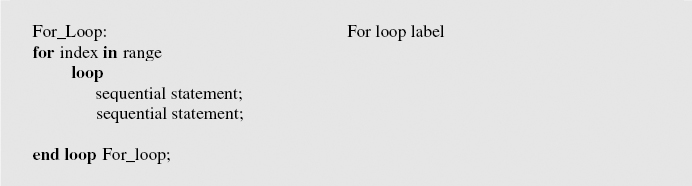

A for loop is a sequential statement that allows a designer to specify a fixed number of iterations in a behavioral design description. It is important to note that in VHDL, unlike other software programs, each iteration occurs concurrently, which means that the loop is “unrolled.” A for loop can be used only inside a sequential statement, such as a process statement, a function, or a procedure. The example in Figure 4.24 illustrates the form of a for statement. A for loop executes the sequential statement within its body each time the index of the loop changes its value within the range of the loop. The label of the for loop is optional; the user may choose not to include it.

Figure 4.24 For Loop

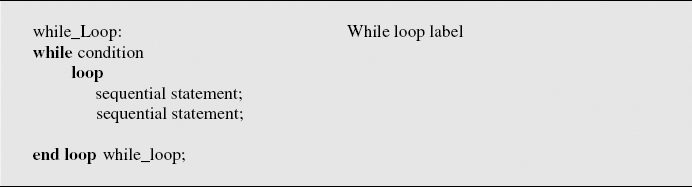

Figure 4.25 While Loop

4.11.2 While Loop

A while loop is another form of sequential loop statement that specifies the conditions under which the loop should continue rather than specifying a discrete number of iterations. The condition ...

Get Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.