1.7 SIMPLE PROGRAMMABLE LOGIC DEVICES

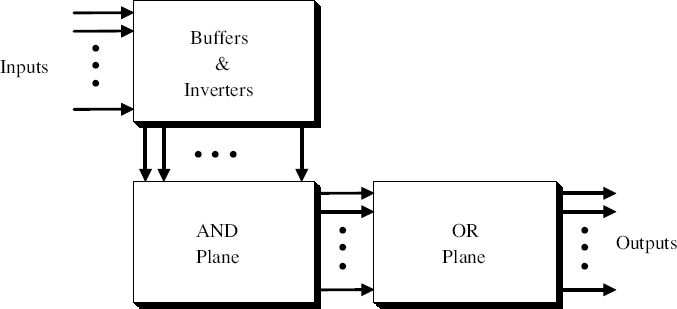

Simple programmable logic devices (SPLDs) include programmable logic arrays (PLAs) and programmable array logic (PALs). Early SPLDs were simple and consisted of an array of AND gates driving an array of OR gates. An AND gate (known as an AND plane or AND array) feeds a set of OR gates (an OR plane). This helps in realizing a function in the sum-of-products form.

Figure 1.1 shows the general architecture of PLAs and PALs. The most common housing of PLAs and PALs was a 20-pin dual-in-line package (DIP). The difference between PALs and PLAs is that in PLA, both the AND and OR planes are programmable, whereas in PALs, the AND plane is programmable but the OR plane is fixed. PLAs were expensive to manufacture and offered somewhat poor performances, due to propagation delays. Therefore, PALs were introduced for their ease of manufacturability, lower cost of production, and better performance. PALs usually contain flip-flops connected to the OR gates to implement sequential circuits. Both PLAs and PALs use antifuse switches, which remain in a high-impedance state until programmed into a low-impedance (fused) state. These devices are generally programmed only once. Generic array logic devices (GALs) are similar to PALs but can be reprogrammed. PLAs, PALs, and GALs are programmed using a PAL programmer device (a burner).

Figure 1.1 Schematic Structure ...

Get Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.