F.2 OUTLINE OF THE SCHEDULING ALGORITHM

The bit-serial scheduling algorithm consists of assigning a “schedule time” to every operator in a bit-serial architecture. This time represents the time when the operation will nominally take place. Informally, each operator must be scheduled at a time after all of its inputs become available (i.e., they have been generated by a previous operator). The scheduling problem can be formulated as a linear programming problem and because all scheduled time of the operators must be integers, the scheduling algorithm must find the optimal integer solution to this problem.

Consider a pair of operators joined by an edge as shown in Fig. F.3. One of the outputs produced by the operator OPi is the operand OPNDx. This operand in turn is the input to the operator OPj (and possibly to others). The scheduled times of operators OPi and OPj are denoted by Ti and Tj respectively. The timing specifications of the relevant output and input ports of OPi and OPj are denoted by ti and tj, respectively.

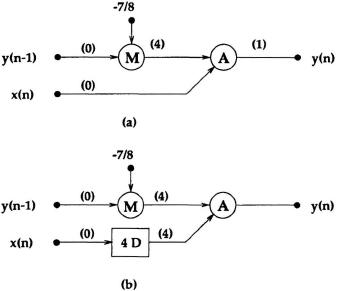

Fig. F.2 Example of the bit-serial scheduling problem. (a) DFG prior to scheduling. (b) DFG after scheduling showing allocated synchronization registers.

Since OPi is scheduled at time Ti, the output OPNDx will become available at time Ti + ti as shown. Further, this same operand will be required as an input to the operator OPj at time Tj + tj. By the requirement ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.