6.4 REGISTER MINIMIZATION IN FOLDED ARCHITECTURES

The register minimization techniques described in Section 6.3 can be used to synthesize control circuits in folded architectures that use the minimum possible number of registers. The basic procedure is as follows:

- Perform retiming for folding (see Section 6.2).

Fig. 6.12 The architecture corresponding to the allocation table in Fig. 6.10(b) for the 3 × 3 matrix transposer.

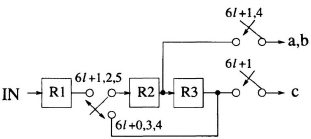

Fig. 6.13 The architecture corresponding to the allocation table in Fig. 6.11(b).

- Write the folding equations (see Section 6.2).

- Use the folding equations to construct a lifetime table.

- Draw the lifetime chart and determine the required number of registers (see Section 6.3.1).

- Perform forward-backward register allocation (see Section 6.3.2).

- Draw the folded architecture that uses the minimum number of registers.

This procedure is demonstrated in this section with 2 examples.

6.4.1 Biquad Filter Example

In this example, a minimum-register architecture is constructed for the DFG in Fig. 6.5. The DFG after retiming for folding is shown in Fig. 6.3, and the folding equations for this DFG are given in (6.2). The folded architecture without any register minimization is shown in Fig. 6.4. This architecture uses 6 registers (the 3 pipelining registers that ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.