Use of the LTR and STR Instructions

General

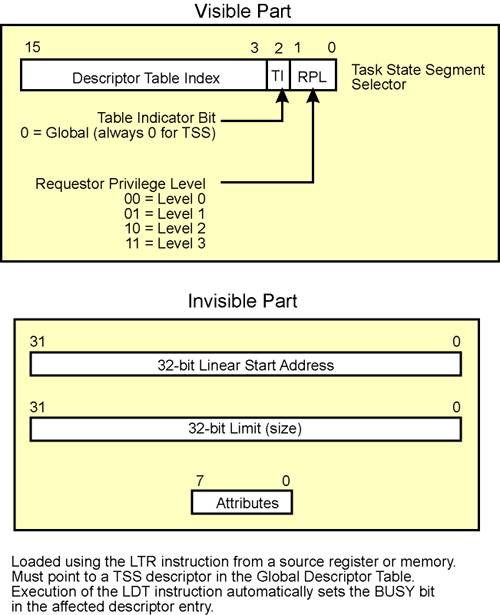

The processor uses the TR (Task Register) to determine the base address and limit of the TSS associated with the current task. The TR is illustrated in Figure 10-6 on page 189.

Figure 10-6. The Task Register

Loading a new 16-bit value into the TR causes the processor to read the TSS descriptor from the GDT entry selected by the TR index field into the invisible part of the TR. When initially loaded with a 16-bit value, the processor uses that value to select an entry in the GDT (the selected entry must contain a TSS descriptor). If it contains any other type of descriptor, or if the selected TSS descriptor ...

Get The Unabridged Pentium 4 IA32 Processor Genealogy now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.