9.2 INSTRUCTION SET PROCESSORS

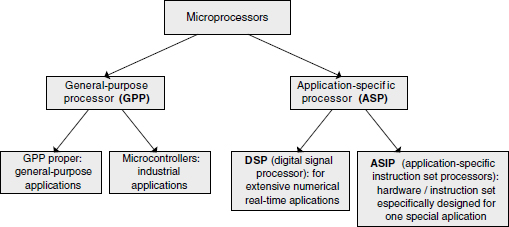

This section is devoted to architectures that execute a reduced set of instructions (reduced instruction set computer—RISC). Belonging to this category are processors, microprocessors, digital signal processors (DSPs), application specific instruction set processors (ASIPs), and others. A first classification of microprocessors is presented in Figure 9.6; it is based on the levels of specialization.

Figure 9.6 Classification of microprocessors according to level of specialization.

The first microprocessors were sequential processors based on Von Neumann architecture. Initially, poor compilers and the lack of processor-memory bandwidth resulted in complex instruction sets: complex instruction set computers (CISCs). In the early 1980s, developments of RISC and VLSI technologies enabled the implementation of pipelined architectures, larger register banks, and more address space in a single-chip processor. In the 1990s the focus was on the exploitation of instruction-level parallelism, which eventually resulted in the modern general-purpose processors (GPPs). Superscalar processors and very long instruction word (VLIW) architectures are examples of dynamic and static parallelism.

An important dimension in processor architectures is the application orientation that has led to a variety of different types of instruction sets and organizations. Today, together ...

Get Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.