8.13. SYSTEM CLOCKING CONSIDERATIONS

The RapidIO parallel physical interface can be deployed in a variety of system configurations. A fundamental aspect to the successful deployment of RapidIO is clock distribution. This section is provided to point out the issues of distributing clocks in a system.

8.13.1. Example Clock Distribution

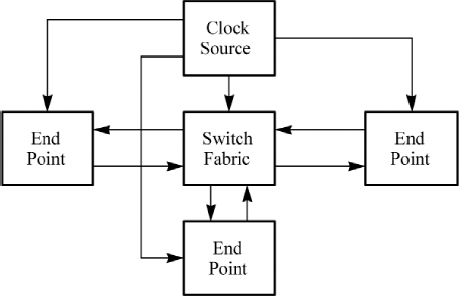

Clock distribution in a small system is straightforward (Figure 8.19). In small systems, clocking is typically provided from a single clock source. In this case the timing budget must account for any skew and jitter component between each point. Skew and jitter are introduced by the end point clock regeneration circuitry (PLL or DLL) and by transmission line effects.

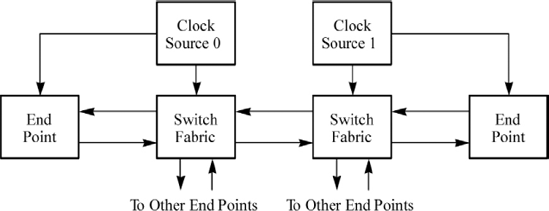

Distributing a clock from a central source may not be practical in larger or more robust systems. In these cases it may be more desirable to have multiple clock sources or to distribute the clock through the interconnect. Figure 8.20 displays the distribution of multiple clocks in a larger system.

Figure 8.19. Clock distribution in a small system

Figure 8.20. Clock distribution in a larger system

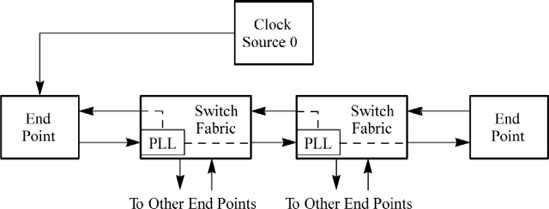

Figure 8.21. Clock distribution through the interconnect

In such a system the clock sources ...

Get RapidIO: The Next Generation Communication Fabric For Embedded Application now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.