2.15. OPERATION LATENCY

In memory transaction environments, where processors or other devices are dependent on the results of an operation before proceeding, latency becomes a key factor to system performance. For latency-sensitive environments the parallel RapidIO interface is preferred. Serial RapidIO will offer higher, and in some cases significantly higher latencies than that offered by parallel RapidIO or traditional buses. It is assumed that the operations of interest here are small byte or cache-line-oriented operations. Since a RapidIO interface is narrower than traditional parallel buses, an operation will require more clock cycles for data transmission; RapidIO also has extra overhead associated with routing and error management. However relative to a bus RapidIO has virtually no contention or arbitration overhead, a significantly higher operating frequency, and a separate and concurrent reply path.

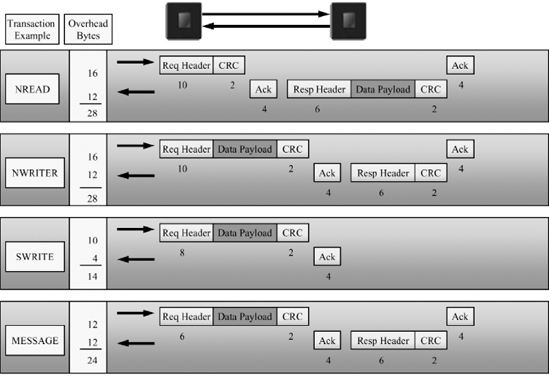

Figure 2.6. Operation overhead includes the total number of bytes sent in each direction to complete an operation (assumes 8-bit route and 32-bit offset address)

While there is complexity and additional latency created by converting a memory or message transaction into a RapidIO packet, the simplicity of the RapidIO protocol ensures that this conversion process can be accomplished in times of the order of 100 nanoseconds in commonly available technologies. Latency through ...

Get RapidIO: The Next Generation Communication Fabric For Embedded Application now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.