11.3.2.3 HSUPA Channels

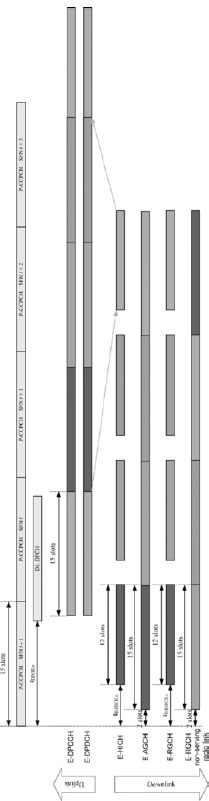

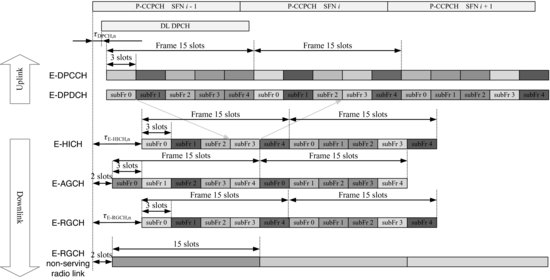

The example of timing of HSUPA channels for E-DCH TTI = 10 ms is depicted in Figure 11.84, and for E-DCH TTI = 2 ms in Figure 11.85.

Figure 11.84 Timing of HSUPA channels. TTI = 10 ms (15 slots)

Figure 11.85 Timing of HSUPA channels. TTI = 2 ms (3 slots)

E-DPDCH carrying E-DCH data and E-DPCCH carrying E-DCH control information are always transmitted simultaneously, except the case of DTX when E-DPCCH is transmitted without E-DPDCH. After E-DPDCH decoding the feedback information (ACK/NACK) is sent by Node B to UE over E-HICH. The transmit timing of the start of the E-HICH frame (in case of 10 ms TTI) or sub-frame (in case of 2 ms TTI) depends on E-DCH TTI length and downlink DPCH delay.

When the E-DCH TTI is 10 ms the E-HICH frame offset relative to P-CCPCH shall be τE-HICH,n chips with:

where τDPCH,n is the downlink DPCH offset relative to P-CCPCH, τDPCH,n is a multiple of 256 chips, that is, τDPCH,n = Tn × 256 chips, Tn ∈ {0, 1, …, 149}.

The P-CCPCH, on which the cell system frame number (SFN) is transmitted, is used as timing reference for all the physical channels. For each cell in the E-DCH active set, the UE shall associate the control data ...