PROBLEMS

4.1 Describe the basic CAD tools for logic design.

4.2 Describe the major design entry tools.

4.3 What is the difference between simulation and synthesis?

4.4 Why should the designer perform a function simulation before final hardware implementation?

4.5 What is VHDL?

4.6 Describe the basic programming structure of VHDL code.

4.7 What is the difference between an entity declaration and an architecture declaration?

4.8 Can an entity have more than one architecture?

4.9 What is a VHDL signal statement? What is it used for?

4.10 What is the function of the “when others” clause in a case statement?

4.11 Describe the difference between the process and generate statements.

4.12 What is the difference between a VHDL component and a VHDL package?

4.13 Write VHDL code to implement a XOR logic gate.

4.14 Write VHDL code to implement a NOR logic gate.

4.15 Write VHDL code to implement a NXOR logic gate.

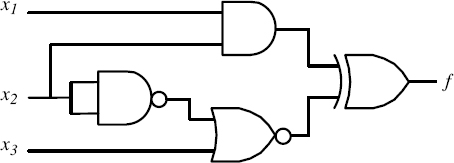

4.16 Write VHDL code to implement the logic circuit in Figure P4.16.

4.17 Write VHDL code to implement the logic circuit in Figure P4.16 using signal data objects.

Figure P4.16

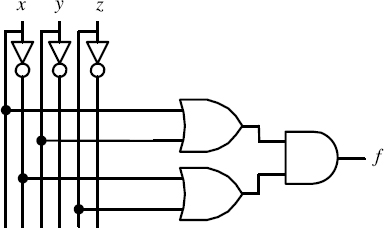

4.18 Write VHDL code to implement the logic circuit in Figure P4.18.

Figure P4.18

4.19 Write VHDL code to implement the logic circuit in Figure P4.18 using signal data objects.

4.20 Write VHDL code to implement ...

Get Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.