CHAPTER 23

DIRECT DIGITAL FREQUENCY SYNTHESIS

DDFS (direct digital frequency synthesis) is a scheme that uses digital circuits and a DAC to generate tunable analog waveforms from a single fixed clock source. In this chapter, we implement this scheme and treat this circuit as a specialized Nios II peripheral. Since only the audio-frequency DACs (within the WM8731 codec device) are available on a DE1 board, we use the DDFS circuit as a sound and music synthesizer.

23.1 INTRODUCTION

Many communication-related applications need to generate a waveform of specific frequency and phase. DDFS is a method of producing a frequency- and phase-tunable digital or analog waveforms from a single fixed clock source. The data points of the waveform are first generated in digital format and then converted to analog format by using a DAC and a low-pass filter. Since the operations within a DDFS circuit are primarily digital, it can offer fast switching among output frequencies, fine frequency resolution, and operation over a wide range of frequencies.

23.2 DESIGN AND IMPLEMENTATION

The DDFS scheme can be used to generate a variety of waveforms. In this section, we examine the synthesis and implementation of three types of waveforms:

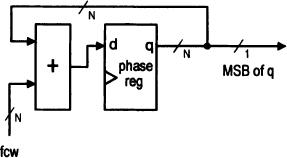

Figure 23.1 Block diagram for synthesizing digital waveform.

- Digital waveform, which is a square wave with constant amplitude.

- Unmodulated analog waveform, typically a ...

Get Embedded SoPC Design with Nios II Processor and Verilog Examples now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.