CHAPTER 9

NIOS II PROCESSOR OVERVIEW

Nios II is Altera's proprietary processor targeted for its FPGA devices. It is configurable and can be trimmed to meet specific needs. In this chapter, we examine its basic organization and key components. The emphasis is on the features that may affect future software and I/O peripheral development.

9.1 INTRODUCTION

Nios II is a soft-core processor targeted for Altera's FPGA devices. As opposed to a fixed prefabricated processor, a soft-core processor is described by HDL codes and then mapped onto FPGA's generic logic cells. This approach offers more flexibility. A soft-core processor can be configured and tuned by adding or removing features on a system-by-system basis to meet performance or cost goals.

The Nios II processor follows the basic design principles of a RISC (reduced instruction set computer) architecture and uses a small, optimized set of instructions. Its main characteristics are:

- Load-store architecture

- Fixed 32-bit instruction format

- 32-bit internal data path

- 32-bit address space

- Memory-mapped I/O space

- 32-level interrupt requests

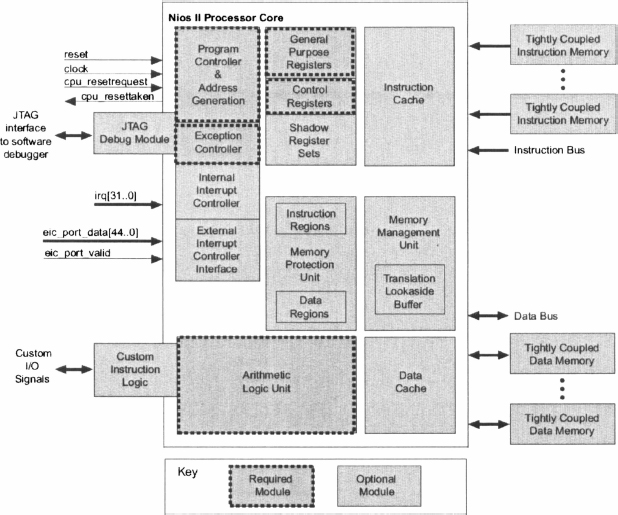

Figure 9.1 Block diagram of a Nios II processor (Courtesy of Altera Corp.).

- 32 general-purpose registers

The conceptual block diagram of a Nios II processor is shown in Figure 9.1. The main blocks are:

- Register file (general purpose registers) and control registers

- ALU (arithmetic and logic unit) ...

Get Embedded SoPC Design with Nios II Processor and Verilog Examples now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.