CHAPTER 6

LOW-ENERGY SYSTEM ISSUES

A large portion of the energy consumption in modern microprocessor designs is in the clock subsystem, including clock generation, distribution, and the final clocked storage-element load. Due to increasing frequency, low skew requirements, and deep pipelining, this clocking energy has been increasing with each processor generation, requiring a more energy-conscious design of the clock subsystem. In this chapter we describe some widely used methods for energy reduction that include supply-voltage scaling, minimizing switched capacitance, minimizing switching activity, and the use of low-swing-circuit techniques. These conventional principles are then applied to the design of alternate topologies of clocked storage elements as well as a general clock distribution network.

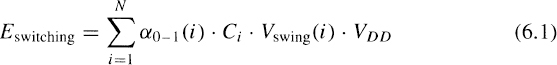

A common design approach for minimizing energy consumption in VLSI systems is to concentrate on reducing the switching component of energy, given by

where N is the number of nodes in the system, Ci is the capacitance at node i, α0-1(i) is the probability that the energy-consuming transition occurs at node i, Vswing is the voltage swing of node i, and VDD is the global supply voltage. Based on this simple formula, the guidelines for reducing energy consumption are simply to minimize each of the terms in the product expression. The most efficient way to minimize energy, as should ...

Get Digital System Clocking: High-Performance and Low-Power Aspects now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.