APPENDIX F

SPICE LEVEL 3 MODEL FOR 0.25 μ M MOSIS PROCESS

F-1 DEVICE MODELS

The device models used in the text were supplied by MOSIS, a supplier of prototyping and small-volume production services for VLSI circuit development. Since 1981, MOSIS has fabricated more than 50,000 circuit designs for commercial firms, government agencies, and research and educational institutions around the world. MOSIS provides access to a wide variety of semiconductor processes offered by multiple silicon foundries.

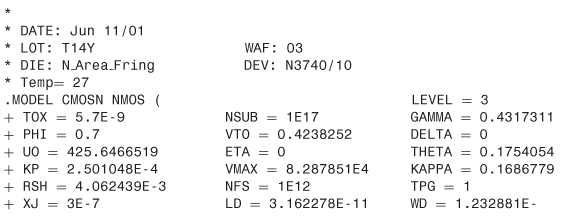

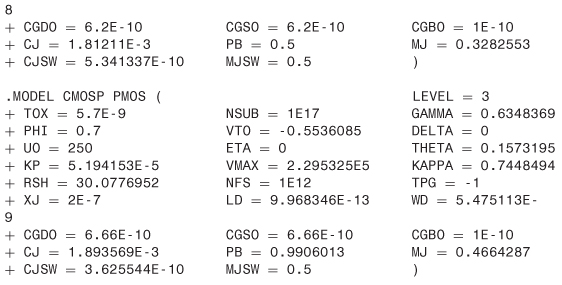

The NMOS and PMOS level 3 device models shown below were used for all transistor level simulation and analysis examples and problems in this text.

REFERENCE

The MOSIS Service, SPICE Level 3 Model Parameters for Classroom Instructional Purposes TSMC (0.25 micron), available at http://www.mosis.com/Technical/Testdata/tl4y_tsmc_025_level3.txt.